**SVP-716**

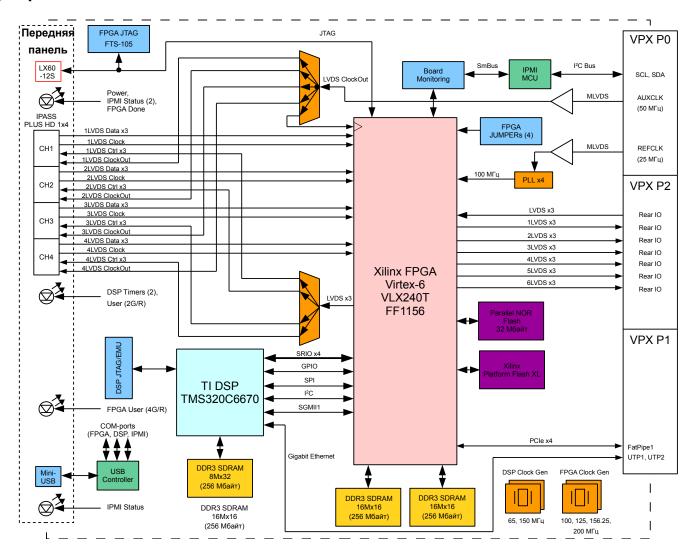

Модуль цифровой обработки данных на базе FPGA Xilinx Virtex-6 и DSP форм-фактора VPX 3U

# Основные особенности

- Высокопроизводительная FPGA Xilinx Virtex-6 семейства LXT/SXT в корпусе FF1156 с поддержкой кристаллов вплоть до VLX365T

- Память FPGA два 16-и разрядных банка DDR3 SDRAM по 256 Мбайт каждый

- Четырёхъядерный DSP C6670 Texas Instruments (TI) с тактовой частотой 1,2 ГГц и набором сопроцессоров и ускорителей

- Память DSP 64-х разрядный банк DDR3 SDRAM 256 Мбайт

- Модуль форм-фактора VPX 3U, соответствующий стандартам: ANSI/VITA 46.0-2013 (воздушное охлаждение), ANSI/VITA 46.3-2012, ANSI/VITA 46.6-2013 и ANSI/VITA 65-2010 (R2012)

- Цифровой порт сигналов LVDS передней панели на разъёме iPass+ HD 4x

- Системные интерфейсы: PCI Express x4 2.0 / Serial RapidIO x4, двухканальный Gigabit Ethernet

- Шина тыльного ввода/вывода LVDS на разъёме VPX P2

# Обзор модуля

#### Особенности

Модуль SVP-716 форм-фактора VPX 3U реализует тандем высокопроизводительной FPGA Xilinx Virtex-6 и многоядерного DSP C6670 TI и предоставляет пользователю уникальное сочетание возможностей параллельной цифровой обработки сигналов на FPGA и алгоритмической гибкости и мощности четырехядерного DSP, являющегося, ко всему прочему, системой на кристалле с набором встроенных сопроцессоров цифровой обработки сигналов и сетевых ускорителей.

#### Производительность

Наряду с высокой производительностью модуль имеет развитые системные интерфейсы: два канала Gigabit Ethernet через порты Ultra-TP1, UTP2 и, настраиваемый пользователем, канал PCI Express 2.0 х4 / Serial RapidIO х4 через порт Fat Pipe 1. Модуль предоставляет пользователю возможность организации межплатного взаимодействия, либо ввода/вывода высокоскоростных сигналов модуля тыльного расширения через шину LVDS на разъёме P2 VPX. Цифровой порт iPass+ HD 4x Moleх на передней панели предназначен для приёма данных LVDS от внешнего удаленного источника цифровых данных, в т. ч. АЦП.

### Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плат, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных и военных применений.

Модуль SVP-716 предназначен для приложений, требующих предельно высокую производительность цифровой обработки данных в реальном времени: фильтрации, спектральных преобразований, корреляционной обработки, кодирования/декодирования, работы с пакетами и т. д. Так, пиковая производительность обработки FPGA модуля на целочисленных операциях умножить-аккумулировать достигает 800 млрд./с (VSX315T, операнды 25 × 18 бит, аккумулятор 48 бит), а производительность DSP составляет свыше 150 GMAC / 75 GFLOPS.

# Функциональная блок-схема

# Технические характеристики

#### DSP

Один DSP (цифровой сигнальный процессор) TI TMS320C6670 (четыре ядра на частоте 1,2 ГГц):

- до 153,6 млрд. операций в секунду над операндами с фиксированной запятой;

- до 76,8 млрд. операций в секунду над операндами с плавающей запятой;

- кэш-память 32 кбайт L1P, 32 кбайт L1D, 1 Мбайт L2 на каждое ядро:

- 2 Мбайта разделяемой памяти уровня L2 (MSMC);

- три аппаратных турбодекодера для WCDMA / HSPA / HSPA+ / TD-SCDMA, LTE, WiMAX на скоростях до 548 Мбит/с;

- турбокодер LTE, WCDMA на скорости до 500 Мбит/с;

- четыре декодера Viterbi с поддержкой скорости декодирования до 38 Мбит/с на 40-разрядных блоках;

- два приемных, один передающий ускорители-сопроцессоры стандарта WCDMA;

- три сопроцессора БПФ (2048 точек 4,8 мкс);

- сопроцессор битовой обработки сигналов стандартов WCDMA / HSPA+, TD-SCDMA, LTE, WiMAX со скоростями до 914 Мбит/с для LTE и 405 Мбит/с для CDMA;

- сетевой сопроцессор с поддержкой алгоритмов аппаратного шифрования ECB, CBCm CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA1/2 (256 бит), MD5 на скоростях до 2,8 Гбит/с для приложений IPSec, SRTP, 3GPP, WiMAX Air и SSL / TLS;

- четыре ускорителя RSA для WCDMA Rel'99, HSDPA, HSDPA+ с поддержкой декодирования Рида-Мюллера.

### FPGA

Особенности FPGA Xilinx Virtex-6 семейства LXT/SXT в корпусе FF1156 с поддержкой кристаллов вплоть до VLX365T:

- до 56880 ячеек Virtex-6;

- до 1344 блоков Virtex-6;

- до 704 блоков RAM Xilinx BlockRAM по 18 кбит общим объёмом 25344 кбит;

- до 12 блоков управления тактированием Virtex-6 MMCM.

### Память FPGA

Два независимых 16-ти разрядных банка памяти DDR3-800 SDRAM объёмом до 256 Мбайт каждый

NOR Flash 16 бит, объёмом 32 Мбайт, выборка 110 нс

Память Platform Flash XL хранения конфигурации FPGA объёмом 128 Мбит, скорость чтения 640 Мбит/с

#### Память DSP

64-х разрядный банк памяти DDR3-1333 SDRAM объёмом 256 Мбайт SPI NOR Flash, объёмом 16 Мбайт

I<sup>2</sup>C EEPROM 128 кбайт для первоначальной загрузки

### Отладочные интерфейсы (внутренние разъёмы)

Консольные COM-порты для каждого из процессора DSP Интерфейс внешнего эмулятора XDS560

# Соответствие стандартам

ANSI/VITA 46.0-2013 VPX Base Standard

ANSI/VITA 46.3-2012 Serial RapidIO on VPX Fabric Connector

ANSI/VITA 46.6-2013 Gigabit Ethernet Control Plane on VPX

ANSI/VITA 65-2010 (R2012) OpenVPX System Standard

#### Разъёмы VPX

#### Разъём Р0:

- сигналы тактирования REF\_CLK;

- сигналы тактирования AUX CLK;

- сигналы I<sup>2</sup>C ко входам SCL и SDA.

#### Разъём Р1:

- порт FatPipe1 может быть сконфигурирован одним из следующих вариантов:

- либо канал PCI Express x1/x4 2.0 (аппаратное ядро PCIe Xilinx + GTX Xilinx);

- либо канал Serial RapidIO x1/x4 до 3,125 Гбит/с (программное IP-ядро Core Xilinx + GTX Xilinx).

- порт UTP1:

- Gigabit Ethernet через порт MAC0 DSP.

- порт UTP2:

- Gigabit Ethernet FPGA (встроенный MAC + GTX Xilinx).

#### Разъём Р2:

21 двунаправленная линия LVDS до 500 Мбит/с, либо 42 линии LVCMOS 2,5 В до 50 МГц, конфигурируемые в FPGA.

#### Порт ввода/вывода iPass+ HD на передней панели

Четыре секции с набором сигналов стандарта LVDS в каждой:

- сигналы на передачу (идентичны для всех секций): три линии данных до 200 Мбит/с + линия тактирования до 100 МГц (разветвленный сигнал AUX\_CLK VPX);

- сигналы на приём (независимые для каждой секции): три линии данных до 1 Гбит/с + линия сопровождающего тактирования до 500 МГц.

Расположение и назначение контактов разъёма Mini-SAS HD, длина кабелей от 0,5 до 10 м

## Отладочные интерфейсы

Порт JTAG FPGA, буферизованный, 3,3 В (разъём передней панели LX60-12S)

Порт JTAG/эмулятора DSP (внутренний разъём TI 60 конт.)

Консольные COM-порты FPGA и DSP с реализацией USB 2.0 (разъём Mini-USB передней панели)

### Энергопотребление

Потребляемая мощность модуля обработки данных не более 50 Вт Распределение потребляемой мощности по линии питания: +12 В (VS1): до 4 A (50 Вт) (определяется загрузкой FPGA, DSP)

#### Условия эксплуатации

Охлаждение: принудительное воздушное

Диапазон рабочих температур: коммерческий (0...+50 °C) или индустриальный (-40...+85 °C)

Температура хранения: −50...+85 °C

Влажность: 10-98 % без конденсата

Возможность нанесения влагозащитного покрытия для жёстких условий

#### Размеры

Форм-фактор: VPX 3U

Размеры:  $160 \times 100 \times 25,06$  мм

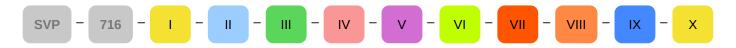

# Информация для заказа

В комплект поставки входят 4 шт. соединительных кабелей порта передней панели (серия Mini-SAS HD 2.1 4x Molex) длиной от 0,5 м до 10 м с шагом 1 м. Программное обеспечение поддержки модуля, а также средства отладки в комплект поставки не входят, их приобретение оговаривается отдельно. Адаптер порта JTAG FPGA для кабеля Xilinx Platfrom Cable USB входит в комплект поставки.

Возможна поставка модуля в другом температурном диапазоне по согласованию.

Основная FPGA Xilinx

Virtex-6

FM130T1:

XC6VLX130T-1

FM315T2:

XC6VSX315T-2

FM130T2:

XC6VLX130T-2

FM365T1:

XC6VLX365T-1

FM240T1:

XC6VLX240T-1

FM365T2:

XC6VLX365T-2

**FM240T2**: XC6VLX240T-2 **FM315T1**: XC6VSX315T-1

Установленный DSP Texas Instruments

**DSP6670C100:** TMS320C6670 с тактовой частотой 1000 МГц

**DSP6670C100X:** TMS320C6670 с тактовой частотой 1000 МГц, с поддержкой

шифрования

Ш

**DSP6670C120:** TMS320C6670 с тактовой частотой 1200 МГц

DSP6670C120X: TMS320C6670 с тактовой частотой 1200 МГц, с поддержкой

шифрования

Объём установленной памяти FPGA

**RFM2x8Mx16/800:** 256 Мбайт в двух 16-ти разрядных банках **RFM2x16Mx16/800:** 512 Мбайт в двух 16-ти разрядных банках

Объём установленной памяти DSP

RDSP1x8Mx32/1333: 256 Мбайт в одном 32-х разрядном банке памяти DDR3-1333

RDSP1x16Mx32/1333: 512 Мбайт в одном 32-х разрядном банке памяти DDR3-1333

Объём памяти NOR FLASH FPGA

**DNFF1x256:** 1 × 256 Мбит **DNFF1x512:** 1 × 512 Мбит **DNFF1x1024:** 1 × 1024 Мбит

Длина соединительных кабелей портов LVDS передней панели

LMS0: Кабели в комплекте поставки отсутствуют

**LMS05**: 5 метров

**LMSNN:** Заказная длина кабелей в целочисленных метрах, где NN — значение от 01 до 10, соответствует длине кабеля от 1 до 10 м с шагом 1 м

Опорное тактирование встроенного синтезатора частоты 100 МГц

**REF0:** Тактирование от встроенного резонатора 25 МГц **REF1:** Тактирование сигналом REF\_CLK VPX 25 МГц

VIII Исполнение (температурный диапазон)

**Т0:** Коммерческое (0...+50 °C) **Т1:** Индустриальное (-40...+85 °C)

IX

**CV1:** С влагозащитным покрытием **CV0:** Без влагозащитного покрытия

Х Передняя панель

FP2: Установлена стандартная передняя панель FMC

**FPN:** Заказная передняя панель, тип устанавливаемого субмодуля оговаривается при заказе дополнительно

Возможны другие конфигурации модуля по индивидуальному запросу. За дополнительной информацией обращайтесь в SET.

# Контактная информация

ЗАО «Скан Инжиниринг Телеком» Россия, 394030, г. Воронеж, ул. Свободы, 75 Тел.: +7 (473) 272-71-01, факс.: +7 (473) 251-21-99 www.setdsp.ru

Электронная почта:

Отдел продаж: sales@setdsp.ru

OOO «Скан Инжиниринг Телеком - СПб» Россия, 199106, г. Санкт-Петербург, 22-я линия В.О., д. 3, корп. 1, лит. М. Тел.: +7 (812) 406-99-95, +7 (812) 406-99-96 www.setdsp.ru

Электронная почта:

Отдел продаж: sales.spb@setdsp.ru

3AO «Скан Инжиниринг Телеком». Все права защищены. © 1991–2018 Документ DS-SVP-716 1.0 создан в ООО «Скан Инжиниринг Телеком - СПб». Все права защищены. © 2018