XDSP-57

Модуль цифровой обработки данных на базе FPGA Xilinx Virtex-4 с двухканальным аналого-цифровым преобразованием с поддержкой системного интерфейса PCI 32/64 бита 33/66 МГц форм-фактора CompactPCI 3U

### Основные особенности

- Основная FPGA Xilinx Virtex-4 семейства VLX или VSX в корпусе FF1148

- Интерфейсная FPGA Xilinx Virtex-4 семейства VLX или VSX в корпусе FF668

- Двухканальное аналого-цифровое преобразование

- Четыре банка памяти высокоскоростной статической RAM ZBT SRAM на FPGA, объёмом 9 Мбайт каждый

- Модуль форм-фактора CompactPCI 3U шириной 4HP с системным интерфейсом PCI 32/64 бита/33 МГц

# Обзор модуля

#### Особенности

Модуль XDSP-57 форм-фактора CompactPCI 3U разработан на основе двух высокопроизводительных FPGA Xilinx: основной Virtex-4 семейств VLX и VSX в корпусе FF1148 с большим объёмом внешней памяти и интерфейсной Virtex-4 семейств VLX и VSX в корпусе FF668.

Интеграцию модуля с остальными модулями CompactPCI нашего производства облегчает наличие дуплексного канала LVDS с производительностью не менее 800 Мбит/с в каждую сторону.

#### Высокая производительность

Модуль XDSP-57 разработан для приложений, требующих высокую производительность, высокую скорость передачи данных и низкую латентность. Модуль использует максимум возможностей FPGA Xilinx Virtex-4.

#### Области применения

Модуль-ускоритель обработки данных XDSP-57 предназначен для выполнения двухканального аналого-цифрового преобразования видео- и радиосигналов с частотой дискретизации до 210 МГц с их последующей цифровой обработкой на базе FPGA Xilinx серии Virtex-4. Модуль предоставляет производителям оборудования высокоэффективное решение для широкого диапазона задач: цифровой радиоприём, радиолокация и радиоизмерения.

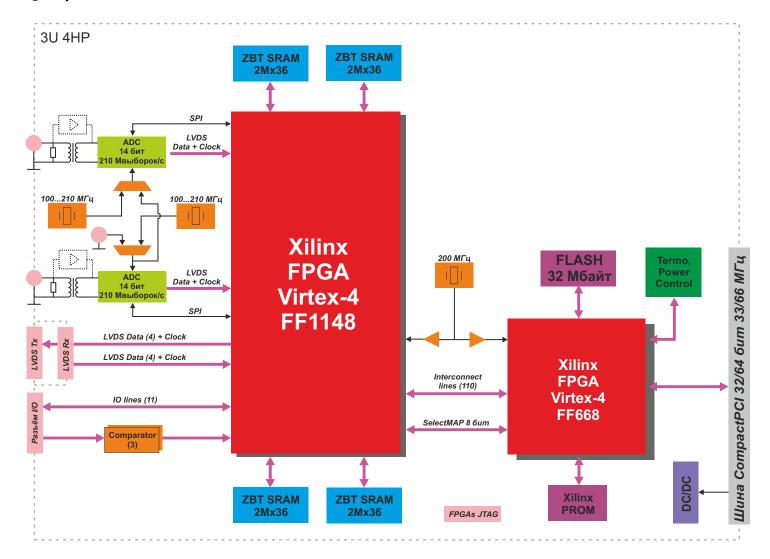

## Функциональная блок-схема

## Технические характеристики

#### **FPGA**

Основная Xilinx Virtex-4 в корпусе FF1148 из ряда:

- XC4VLX40, XC4VLX60, XC4VLX80, XC4VLX100, XC4VLX160;

- XC4VSX55.

Особенности основных FPGA:

- до 152064 ячеек Virtex-4;

- до 288 блоков Virtex-4;

- до 320 банков RAM Xilinx BlockRAM по 18 кбит общим объёмом 5760 кбит;

- до 8 блоков управления тактированием Virtex-4 DCM.

Интерфейсная Xilinx Virtex-4 в корпусе FF668 из ряда:

XC4VLX25, XC4VLX40, XC4VLX60, XC4VSX35.

Особенности интерфейсных FPGA:

- до 41472 ячеек Virtex-4;

- до 168 блоков Virtex-4;

- до 96 блоков RAM Xilinx BlockRAM по 18 кбит:

- до 8 блоков управления тактированием Virtex-4 DCM.

### Память

Четыре банка синхронного статического RAM ZBT SRAM по 9 Мбайт (2 Мбита × 36) 200 МГц

Энергонезависимая Flash-память хранения файлов конфигурации основной FPGA объёмом (16 Мбита × 16) 32 Мбайт

Энергонезависимая память Platform Flash хранения конфигурации интерфейсной FPGA объёмом 1 Мбайт

#### Аналого-цифровое преобразование

Количество каналов: 2

Разрядность 10 бит

Диапазон частот тактирования 100...200 МГц

Размах входного сигнала 0,5 В (50 Ом), разъём SMA

Размах входного сигнала в полной разрядной сетке, B:

- «открытый» вход: -1...+1±0,05 или 0...+2±0,05;

- «закрытый» вход: 2±0,05.

Предельные уровни входного сигнала, В:

- «открытый» вход:

- −1,8...+2,1 (при выбранном входном диапазоне ±1 В);

- − 0,8...+2,8 (при выбранном входном диапазоне 0...+2 В).

- «закрытый» вход: размах не более 3,5 В.

Динамический диапазон тракта с несущей 200 МГц, при температуре 25 °C, дБ:

- F<sub>in</sub> = 10 МГц 80 дБ;

(Опция)

- F<sub>in</sub> = 70 МГц 70 дБ;

- F<sub>in</sub> = 140 МГц 60 дБ.

Отношение сигнал/шум тракта, с несущей 200 МГц, при температуре 25 °C, дБ:

- F<sub>in</sub> = 10 МГц 65 дБ;

- F<sub>in</sub> = 70 МГц 62 дБ;

- F<sub>in</sub> = 140 МГц 59 дБ.

Возможность программирования коэффициента усиления АЦП, дБ: 0...6 с шагом 1

Выход данных: двоичный дополнительный, либо двоичный прямой

Стандарт выходных данных  $AU\Pi$  — DDR LVDS

#### Соответствие стандартам

PICMG 2.0 Rev 3.0 CompactPCI Base Specification

### Тактирование

Опорный кварцевый генератор 125 МГц/50 ppm, программируемый в диапазоне: 10...250 МГц, шаг 0,1 Гц

#### Энергопотребление

Потребляемая мощность интерфейсного модуля не более 33 Вт

Распределение потребляемой мощности по линиям питания:

- +12 В: до 0,09 A (1,1 Вт);

- -12 В: до 0,09 A (1,1 Вт);

- +5 В: до 4 А (20 Вт);

- +3,3 В: до 3 А (10 Вт).

### Условия эксплуатации

Охлаждение: воздушное

Диапазон рабочих температур: коммерческий (0...+50 °C) или индустриальный (-40...+85 °C)

Температура хранения: -40...+85 °C

Влажность: 10-95 % без конденсата

#### Размеры

Форм-фактор: CompactPCI 3U

Ширина: 4НР

Размеры Mid-Size:  $100 \times 160 \times 30$  мм

# Информация для заказа

Основная FPGA Xilinx

Virtex-4 в корпусе FF1148

FM40: XC4VLX40

FM60: XC4VLX60 FM80: XC4VLX80

FM100: XC4VLX100 FM160: XC4VLX160 FM55: XC4VSX55

Служебная FPGA Xilinx

Virtex-4 в корпусе FF668

**FS25**: XC4VLX25 **FS40**: XC4VLX40

**FS60:** XC4VLX60 **FS35:** XC4VSX35

Исполнение (температурный диапазон)

**Т0:** Коммерческое (0...+50 °C) **Т1:** Индустриальное (-40...+85 °C)

Покрытие

**CV0:** Без влагозащитного покрытия **CV1:** С влагозащитным покрытием

Пример кода изделия: XDSP-57-FM40-FS25-T1-CV1

XDSP-57— Модуль цифровой обработки данных на базе FPGA Xilinx Virtex-4 с двухканальным аналого-цифровым преобразованием с поддержкой системного интерфейса PCI 32/64 бита 33/66 МГц форм-фактора CompactPCI 3U

**Основная FPGA Xilinx:** XC4VLX40 **Служебная FPGA Xilinx:** XC4VLX25

**Исполнение (температурный диапазон):** Индустриальное (-40...+85 °C)

Покрытие: С влагозащитным покрытием

Возможны другие конфигурации модуля по индивидуальному запросу. За дополнительной информацией обращайтесь в SET.

# Контактная информация

ЗАО «Скан Инжиниринг Телеком» Россия, 394030, г. Воронеж, ул. Свободы, 75 Тел.: +7 (473) 272-71-01, факс.: +7 (473) 251-21-99 www.setdsp.ru

Электронная почта:

Отдел продаж: sales@setdsp.ru

ООО «Скан Инжиниринг Телеком - СПб» Россия, 199106, г. Санкт-Петербург, 22-я линия В.О., д. 3, корп. 1, лит. М. Тел.: +7 (812) 406-99-95, +7 (812) 406-99-96 www.setdsp.ru

Электронная почта:

Отдел продаж: sales.spb@setdsp.ru

ЗАО «Скан Инжиниринг Телеком». Все права защищены. © 1991–2018 Документ DS-XDSP-57 1.0 создан в ООО «Скан Инжиниринг Телеком - СПб». Все права защищены. © 2018