Основные характеристики

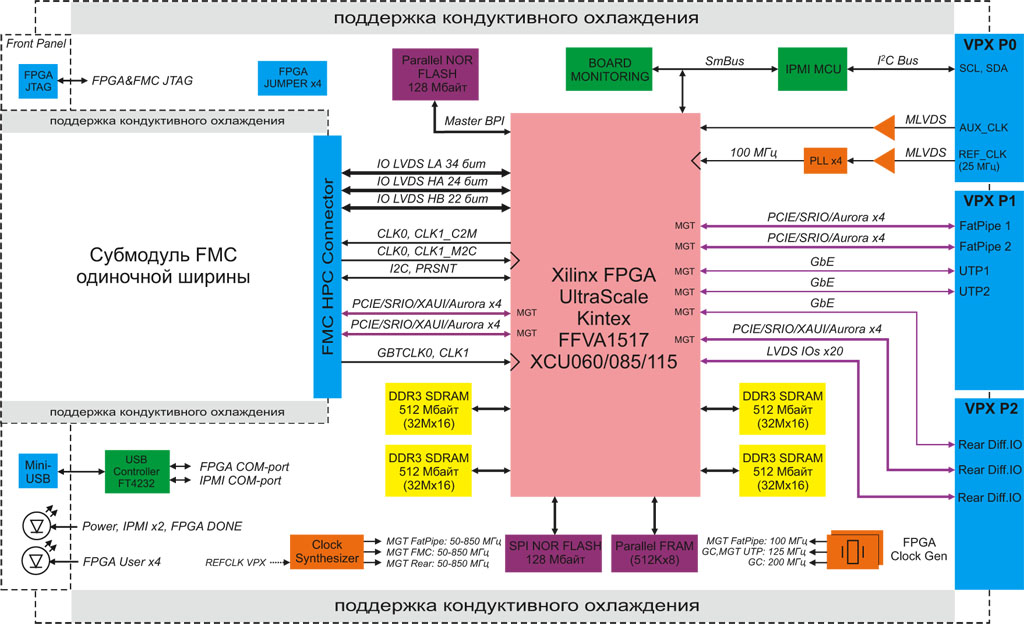

- Высокопроизводительная FPGA Xilinx Kintex UltraScale в корпусе FFVA1517 из ряда XCKU060/085/115 объёмом свыше 1 млн. логических ячеек и числом умножителей свыше 5,5 тысяч

- Четыре независимых

16-ти разрядных банка памяти DDR3 общим объёмом до 2 Гбайт - Установка субмодуля FMC в соответствии со стандартом

ANSI/VITA

57.1-2010 FPGA Mezzanine Card (FMC) Standard с поддержкой HPC интерфейса, включая 8 дуплексных линий MGT - Модуль форм-фактора VPX 3U, соответствующий стандартам:

ANSI/VITA

46.0-2013 (воздушное охлаждение) ANSI/VITA46.3-2012 , ANSI/VITA46.4-2012 , ANSI/VITA46.6-2013 , ANSI/VITA57.1-2010 и ANSI/VITA65-2010 (R2012) - Поддержка системных интерфейсов: PCIe, Gigabit Ethernet, SRIO, Aurora

- Поддержка тыльного модуля ввода/вывода: MGT и LVDS/LVCMOS

- Исполнение с воздушным и кондуктивным охлаждением

Описание

Особенности

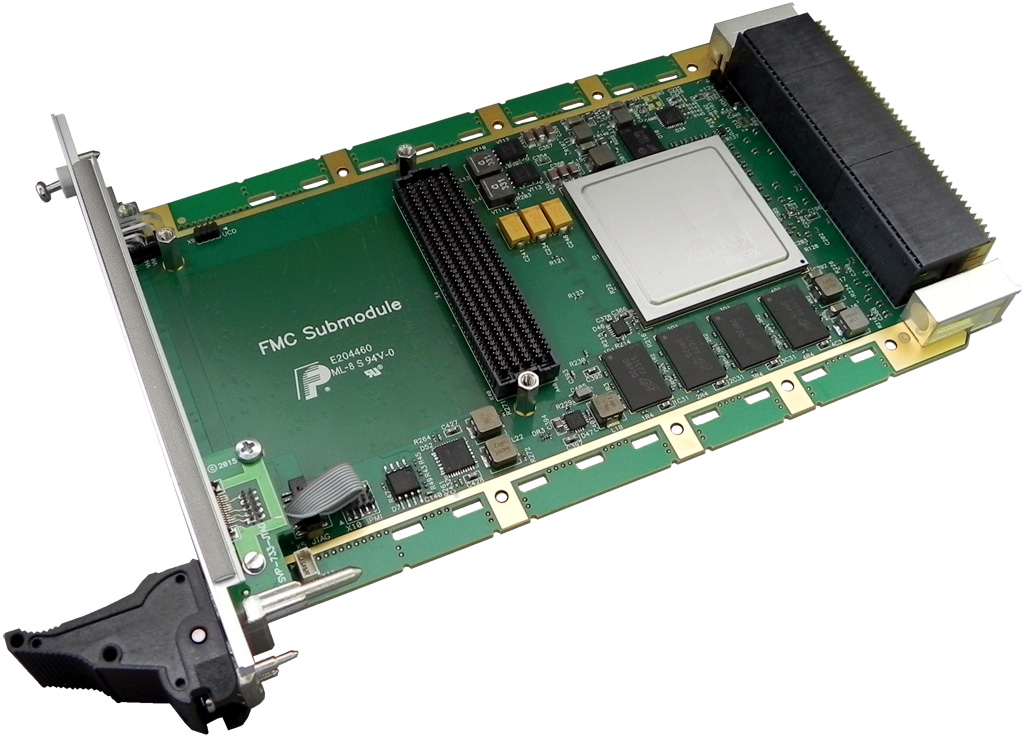

Модуль SVP-733 сочетает богатые возможности цифровой обработки сигналов на базе

микросхемы программируемой логики Kintex UltraScale Xilinx, широкие интерфейсные

возможности с применением последовательных высокоскоростных интерфейсов на базе

трансиверов MGT Xilinx и значительный объём памяти DDR3 в четырех независимых

банках. Реализованная поддержка установки субмодуля FMC стандарта

ANSI/VITA

Модуль SVP-733 предназначен для приложений, требующих предельно высокую

производительность цифровой обработки данных в реальном времени: фильтрации, спектральных

преобразований, корреляционной обработки, кодирования/декодирования, работы с пакетами

и т. д. Пиковая производительность обработки операций на целочисленных операциях

умножить-аккумулировать достигает 3300

Производительность

Наряду с высокой производительностью модуль предоставляет широкие возможности в части

организации системных интерфейсов: поддерживаются два канала FP LAN4

PCIe/SRIO/Aurora (

Пропускная способность интерфейса модуля с субмодулем FMC достигает 80

Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плату, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных и военных применений.