Описание

Предоставляет возможность организации интерфейса взаимодействия FPGA c микросхемой цифро-аналогового преобразователя, установленной на субмодуле FMC.

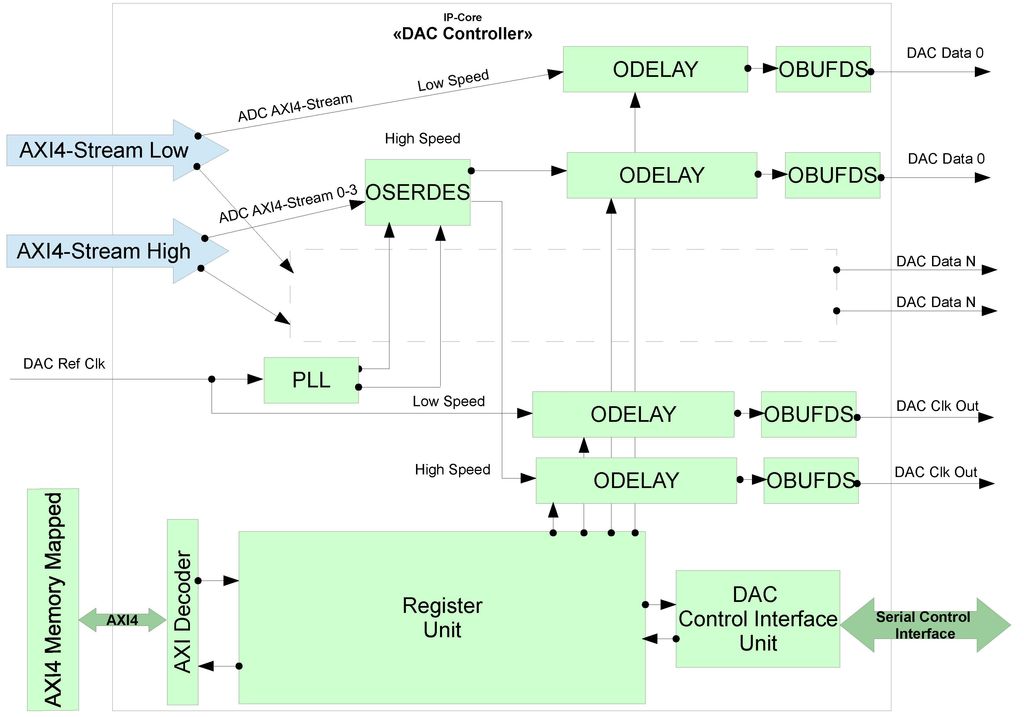

«DAC контроллер» является устройством позволяющим реализовать поддержку работы с ЦАП различных типов и производителей: DAC5878 производства Maxim, DAC5681Z производства Texas Instruments и другими. Основной функционал IP-ядра составляют аппаратные элементы FPGA компенсации разницы во временных задержках на всех физических цепях от FPGA до АЦП, аппаратные элементы конвертации параллельных шин потоков данных ЦАП в формате AXI4-Stream в последовательные данные для вывода потоков данных на ЦАП, а также дополнительные модули для управления ЦАП по последовательным интерфейсам.

Применение

IP-ядро «DAC контроллер» предназначено для максимально быстрой адаптации пользовательских модулей цифровой обработки сигналов для совместной работы с ЦАП.

Применение IP-ядра в качестве строительного блока в решениях, реализуемых на базе FPGA модулей стандартов VPX и AdvancedMC производства ЗАО «Скан Инжиниринг Телеком», позволяет обеспечить полную пропускную способность, масштабируемость и надежность пользовательских проектов.